|

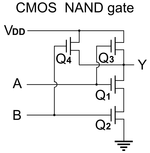

CMOSCMOS(シーモス、Complementary Metal-Oxide-Semiconductor; 相補型MOS)とは、P型とN型のMOSFETをディジタル回路(論理回路)で相補的に利用する回路方式[注釈 1]、およびそのような電子回路やICのことである[1]。また、そこから派生し多義的に多くの用例が観られる(『#その他の用例』参照)。 CMOSプロセスは、フェアチャイルドセミコンダクター社のフランク・ワンラスが考案し、翌1963年にワンラスとチータン・サーが学会で発表したのが始まりである。RCA社は1960年代後半に「COS-MOS」という商標で商品化し[2]、他のメーカーに別の名称を探させ、1970年代前半には「CMOS」が標準的な名称となるに至った。 CMOSは、1980年代にNMOSロジックを抜いてVLSI用MOSFETの主流となり、TTL(Transistor-transistor logic)技術も置き換えた[3]。その後、CMOSはVLSIチップに搭載されるMOSFET半導体デバイスの標準的な製造プロセスであり続けている。2011年現在、ほとんどのデジタル、アナログ、ミックスドシグナルICを含むICチップがCMOS技術で製造されている。 CMOSデバイスの重要な特性は、高い耐ノイズ性と低い静的電力消費である。 MOSFETのペアのうち1つのトランジスタは常にオフであるため、直列の組み合わせはオンとオフを切り替える瞬間に大きな電力を消費するだけである。そのため、NMOSロジックやTTLのように状態変化していないときにも大きな定常電流が流れることはなく発熱が少ないため、高密度に集積できる。CMOSがVLSIチップの実装技術として最も広く使われるようになったのは、主にこのような理由による[4]。 MOSとはMetal(金属)-Oxide(酸化膜)-Semiconductor(半導体)の略で、MOS型電界効果トランジスタの物理的構造のことを指す。酸化膜絶縁体の上に金属ゲート電極を置き、さらにその上に半導体材料を置いたものである[1]。かつてはゲート電極としてアルミニウムが使われていたが、現在はポリシリコンが使われている[5]。IBMやインテルが45ナノメートル・ノード[6]以下のサイズで発表したように、CMOSプロセスにおける「高誘電率(high-k)/金属ゲート」の登場により、一部で金属ゲートが復活している[7]。 CMOSは常にエンハンスメントモードMOSFETを使用する。言い換えれば、ゲート-ソース間電圧がゼロの場合、トランジスタがオフになる[8]。 原理 CMOS回路は、p型とn型の金属-酸化膜-半導体電界効果トランジスタ(MOSFET)を相補的に組み合わせて、論理ゲートやその他のデジタル回路を実装するものである[1]。 最も基本的な論理ゲートであるNOTゲート(論理反転)を右図に示す。この回路において、VddとVssは電源線(VddはVssに対して3〜15V程度の電位差を持つ)で、Aが入力信号線である。Vdd側(図中上側)がPMOS-FETでありVss側(図中下側)がNMOS-FETである。 AがVssと同じ電位を持つとき、上のFETがオンになり、下のFETがオフになる。このため、出力Qの電位はVddとほぼ等しくなる。また、AがVddと同じ電位を持つとき、上のFETがオフになり、下のFETがオンになる。このため、出力Qの電位はVssとほぼ等しくなる。つまり、Aと反対の電位がQに現れる事になる。 歴史相補型回路相補型回路の原理は、1953年にジョージ・クリフォード・シクライによってシクライ・ペア(Sziklai pair)として初めて紹介された。シクライ・ペアは、ダーリントン接続と同様に増幅度を増やしてベース電流を減らすためのものであった。しかし、ダーリントン接続と違ってNPNトランジスタとPNPトランジスタを組み合わせるという相補型バイポーラトランジスタ回路であった[9]。その後、いくつかの相補型回路について議論された。 1962年には、同じくRCA社のポール・K・ウェイマーが、CMOSに近い薄膜トランジスタ(TFT)相補型回路を発明した[10]。彼は、相補型フリップフロップ回路とインバータ回路を発明したが、より複雑な相補型論理の研究はしていない。pチャネルとnチャネルのTFTを同一基板上の回路に入れたのは彼が最初である。その3年前には、ジョン・T・ウォールマークとサンフォード・M・マーカスが、JFETを使った集積回路として、相補型メモリ回路を含むさまざまな複雑な論理機能を発表している。フランク・ワンラスは、RCAでウェイマーが行った研究に精通していた。 MOSFETの登場MOSFET(金属-酸化膜-半導体電界効果トランジスタ、MOSトランジスタ)は、1959年にベル研究所のモハメド・M・アタラ とダウォン・カーンによって発明された[11]。MOSFETの製造プロセスには、もともとPMOS(p型MOS)とNMOS(n型MOS)の2種類があり、いずれもMOSFETを発明した当時のアタラとカーンが1960年にゲート長20μmを開発し、その後10μmのPMOS、NMOSデバイスを開発したものである。MOSFETは当初、バイポーラトランジスタを優先していたベル研究所では見過ごされ無視されていたが、MOSFETの発明はフェアチャイルドセミコンダクターで大きな関心をよんだ。アタラの研究に基づいて、チータン・サーが1960年後半に製造したMOS制御四極真空管でフェアチャイドにMOS技術を導入した[11]。 CMOSの登場PMOSとNMOSの両プロセスを組み合わせた新しいタイプのMOSFETロジックが、フェアチャイルドのフランク・ワンラスとチータン・サーによって開発され、コンプリメンタリーMOS(CMOS)と呼ばれるようになった[12]。1963年2月に論文として発表された。その論文とワンラスが出願した特許では、シリコン基板を熱酸化してドレイン接点とソース接点の間に二酸化ケイ素の層を作ることを基本として、CMOSデバイスの製造方法を概説している。 CMOSは1960年代後半にRCA社によって商業化された。RCAは集積回路(IC)の設計にCMOSを採用し、1965年に空軍のコンピュータのためにCMOS回路を開発し、1968年には288ビットのCMOS SRAMメモリチップを開発した[13]。RCAは1968年に4000シリーズの集積回路にCMOSを採用し、20μmの半導体製造プロセスから始め、その後数年間で10μmのプロセスに徐々に拡張した。当初の4000シリーズは最大1 MHzのクロックでしか動作しなかった。一方、当時のTTLは、10 MHzで動作可能だったので、当時のCMOSは速度性能的に不十分だったことは否めない[2]。 CMOSの発展CMOS技術は、当初アメリカの半導体業界では、当時より高性能だったNMOSを優先して見過ごされていた。しかし、CMOSは低消費電力であることから日本の半導体メーカーにいち早く採用され、さらに進化し、日本の半導体産業の隆盛につながった。東芝は1969年に通常のCMOSよりも低消費電力で高速動作する回路技術C²MOS(Clocked CMOS)を開発した[14]。東芝はC²MOSの技術を用いて、1971年に開発され1972年に発売されたシャープのLEDポケット電卓「エルシーミニ」のLSI(大規模集積回路)チップを開発した。諏訪精工舎(現セイコーエプソン)は1969年からセイコークォーツ腕時計のCMOS ICチップの開発を始め、1971年にセイコーアナログウオッチ38SQWを発売して大量生産を開始した[15]。民生用として初めて量産されたCMOS製品は、1970年に発売されたハミルトンのデジタル腕時計「パルサー タイム・コンピューター」である[16]。消費電力の少なさから、1970年代以降、電卓や時計にCMOSロジックが広く使われるようになった。 1970年代前半の初期のマイクロプロセッサはPMOSロジックで作られており、PMOSロジックが初期のマイクロプロセッサ業界を支配していた。世界初のマイクロコンピュータIntel 4004と世界初の汎用マイクロコントローラTMS1000は、PMOSロジックであった。CMOSを使ったマイクロプロセッサは1975年にIntersil 6100とRCA CDP 1801として登場したが、マイクロプロセッサの世界でCMOSが主流になるのは1980年代に入ってからである。 初期のCMOSはNMOSロジックより遅かったため、1970年代のコンピュータにはNMOSロジックがより広く使用されていた。CMOSメモリチップ Intel 5101(1Kbit SRAM)のアクセス時間は800ns[17]だったのに対し、当時最速のNMOS(HMOS)メモリチップ Intel 2147(4Kbit SRAM)(1976年)のアクセス時間は55/70ns[18]と遥かに高速であった。 1978年、Masuhara Toshiakiが率いる日立の研究チームは、ツインウェルHi-CMOSプロセスを導入し、3μmプロセスで製造したメモリチップ HM6147(4Kbit SRAM)を発表した[19]。HM6147のアクセス時間は35/45/55ns[20]なので、Intel 2147の55/70ns[18]より高速である。HM6147の消費電流は5Vで最大80mA[20]であり、Intel 2147の5Vで最大180mA[18]と比べて大幅に削減することに成功した[注釈 2]。ついにCMOSはNMOSロジックの性能を超えた。同等あるいはそれ以上の性能で消費電力が大幅に少ないツインウェルCMOSプロセスは、最終的にNMOSを抜いて1980年代のコンピュータ用半導体製造プロセスとして最も一般的なものになった。 1989年に木星の軌道を周回したNASAのガリレオ (探査機)は、低消費電力を理由にRCA 1802 CMOSマイクロプロセッサを使用した[21]。 CMOSの進化インテルは1983年にCMOS半導体デバイス製造用の1.5μmプロセスを発表した[22]。1980年代半ばには、IBMのビジャン・ダヴァリが高性能、低電圧、ディープサブミクロンCMOS技術を開発し、より高速なコンピュータや携帯コンピュータ、バッテリー駆動の携帯電子機器の開発を可能にした[23]。 1988年にダヴァリは、高性能250nm CMOSプロセスを実証するIBMチームを率いている[24]。 1987年に富士通が700nmのCMOSプロセスを製品化[22]。1989年に日立、三菱電機、NEC、東芝が500nmのCMOSを製品化[25]。1993年にソニーが350nm、日立とNECが250nmのCMOSを製品化した。1995年に日立が160nmのCMOSプロセスを、1996年に三菱が150nmのCMOSを、1999年にサムスン電子が140nmのCMOSを発表した[25]。 2000年にマイクロン・テクノロジのグルテジ・シン・サンドゥとチュン・T・ドアン(Trung T. Doan)が原子層堆積法High-κ誘電体膜を発明し、コスト効率の良い90nmのCMOSプロセスを開発した[23][26]。2002年に東芝とソニーが65nmのCMOSプロセスを開発し[27]、2004年にTSMCが45nm CMOS論理の開発を始めた[28]。マイクロン・テクノロジのグルテジ・シン・サンドゥによるピッチダブルパターンの開発によって2000年代に30nm級CMOSを開発することになった[23]。 CMOSは現代のほとんどのLSIやVLSIデバイスに用いられている[29]。ワットあたりの性能が最も高いCPUは1976年以来2010年に至るまでCMOSスタティックロジックでありつづけている。 2019年現在、半導体デバイス製造は平板CMOS技術がまだ主流であるが、徐々に20nm以下の半導体ノード製造可能な非平板FinFET技術に取って代わられつつある[30]。 技術解説 Q1,Q2はNMOS、Q3,Q4はPMOSのトランジスタで構成されている。  Q1,Q2はNMOS、Q3,Q4はPMOSのトランジスタで構成されている。 TTLやNMOSロジックやPMOSロジックのようにPNP型あるいはNPN型バイポーラトランジスタの片方だけを利用すると、常に電流が流れつづける。しかし、CMOSでは論理が反転する際にMOSFETのゲートを飽和させる、あるいは飽和状態から電荷を引き抜くための電流しか流れないため、消費電力が少ない[31]。回路設計時にスイッチング回数を減らす工夫をすることで、さらに消費電力の削減ができる。 さらに、微細化によって単一のMOSFETをスイッチングに要する電力量も減少する。これにより、集積度を向上させるだけで、高速化と消費電力の低減が同時に得られる(デナード則。ムーアの法則も参照)[32]。 しかし、商用マイクロプロセッサの生産に使われる最先端の集積回路プロセスでは、21世紀に入った頃から、微細化による漏れ電流の増加による非スイッチング時の消費電力の上昇が、前述の消費電力の低減を上回るようになってしまっている。いわゆる「ムーアの法則の限界」として知られる現象のひとつである[33]。 過去には、CMOSはMOSFETのゲート容量を飽和させる状態まで電流を流しつづけなければスイッチングが行われないため、TTLやNMOSロジックと比較し動作が遅いという弱点があった。しかし、微細化によるゲート容量の低下とVdd-Vssの低減、さらにはゲート電極材料の変更(ポリシリコンの使用)によってこの欠点は克服されている[34]。 TTLに比べて入力インピーダンスが非常に高いため、入力端子に静電気が蓄積しやすい。また、MOSFETは、ゲートに高電圧がかかると絶縁層が放電によって破壊され回復不能となるため、静電気による破損が起きやすい。そのため、通常、クランプダイオードなどの保護回路が設けられる。ただ、近年の集積回路の微細化によって、静電耐性の低下と静電保護対象の入力端子の増加が問題となっている[35]。 →「デジタル回路 § プルアップ・プルダウン」を参照

MOSFETの動作領域における直流伝達特性は、線形領域における出力電圧が入力電圧にほぼ等しいのに対して、飽和領域における出力電圧はゲート電圧からVth「しきい値電圧」を引いた値となる[36]。p-MOSFET が飽和領域のとき n-MOSFET は線形領域であり、n-MOSFET が飽和領域のとき p-MOSFET は線形領域であることより、CMOSの動作領域の殆どを線形領域とすることができる。 CMOS構造にすると、出力電圧範囲は電源電圧範囲に概ね等しくなる。入力信号のしきい値はHの時とLの時で対称となるので、論理回路設計が負論理でも正論理でも電気的な特性に違いがなくなり論理設計の自由度が増す。同時に、電源電圧(動作電圧)の許容範囲も広くなり電気的な設計をしやすくなる。 CMOSは、電源電圧を低くすると消費電力が少なくなる反面、伝達遅延時間が大きくなる性質を持つ。これは、単純な乗除算やせいぜい開平算を、人間のキー操作速度に合わせて行えば良く消費電力は抑えたい電卓などにはもってこいである。一方でその動作の遅さが嫌われるような、たとえば過去には性能第一のスーパーコンピュータやメインフレームはECLが使われていた。しかし、拡大するパーソナルコンピュータ市場による後押しによって微細化が進み、低電圧動作と高速化の両立が図られたことと、集積度の向上や必要な冷却能力の緩和によるトータルコストの低下等の要因によって、コストパフォーマンス的にもECLを凌駕するようになり、今日ではメインフレーム、さらにはスーパーコンピュータ向けマイクロプロセッサ市場でもCMOSが主流となっている[37][38]。 また、同じような理由で半導体メモリなどをはじめとするロジックICもほとんどがCMOS構造で製造されており、近年は小容量電源回路・アナログ-デジタル変換回路・デジタル-アナログ変換回路などを含むものまで製作されるようになっている。 使用上の注意点CMOS構造では、P型半導体とN型半導体が共存するので寄生素子(寄生ダイオード・寄生サイリスタなど)が生じてしまう。このため、何らかの原因で電源電圧範囲を入力電圧が外れると、MOSFETがオンのままとなるラッチアップ現象が発生する。このため、一瞬でも電源電圧範囲を超える可能性がある入力端子には、ダイオードなどによる保護回路を設ける必要がある。なお、これらの保護回路を内蔵したICも存在する(入力トレラント機能)。 入力電圧をHとLの中間にすると、本来両方が同時にオン状態になってはいけない、電源側と接地側の両方のMOSFETがオンになってしまう(かもしれない。電源電圧とMOSFETのスレッショルドに依る)。これにより、最悪の場合電源が接地にショートした格好となり、大電流(貫通電流)が流れる。このとき発生する熱によって、自身が破損してしまうことも多い。このため、入力として使わない(論理的にはどこにも接続する必要がない)入力端子は、電位を不定にしてそのようなことを起こす可能性が無いように、HかLに固定して電位を安定させる必要がある。 CMOS標準ロジックIC汎用ロジックIC(標準ロジックIC)の一群として、CMOSで実装されたICのシリーズがある。この節ではそれらについて説明する。初のシリーズ製品は1968年にRCAから発売された4000シリーズ(CD4000シリーズ)[12]、モトローラから4500シリーズも提供された。後には既存の74シリーズをベースとしたピン配列などに互換性がある74HCシリーズがメジャーである。 4000シリーズは、基本的なゲート回路においてさえ既存のTTLの標準ロジックICとピン配置等が異なったものであるなど[39]、置換えを考慮した設計ではなかった。それでも、多くの会社からセカンドソースが売り出された。4000シリーズの時代には、既にTTL標準ロジックICで設計された基板が多数開発されていたことと、TTL標準ロジックICは量産による低価格化が進んでいたことから、CMOS標準ロジックICは低消費電力や許容幅の広い電源電圧などの、CMOSの特性が生かされる用途に使われるのみにとどまった。 しかし、互換ピン配置等、(電気的な設計にもよるが)TTLとの置き換えが可能な74HCシリーズ(74シリーズと互換性のあるHigh Speed CMOSを表す)が出現し、さらに74HCT(High Speed CMOS TTL compatible)や74ACTのように入力信号の電位条件がTTL互換であり、TTLと直接接続できるタイプが出現するに至った。これによりCMOS標準ロジックは一気に普及し価格も下落したため、現在ではTTL標準ロジックICよりも多く用いられるようになった。

CMOS入出力レベル電圧 (V)

Vdd : 電源電圧(TTL回路の慣例に倣い、Vccと記述されることもある。) その他の用例固体撮像素子の一種であるCMOSイメージセンサを単にCMOSと言う場合がある。固体撮像素子としては、従来はほぼCCDイメージセンサが使われてきたが、近年はCMOSイメージセンサも多用されつつある。 パソコンやワークステーションなどの利用者の間では、BIOSの現在時刻やハードウェア設定情報などを保持するための不揮発性メモリ、またはそのメモリに保持されているデータそのものを指して、単にCMOSと呼ぶこともある。たとえば「マザーボードが起動しなくなったときはCMOSをクリアする」などと使う(不揮発性メモリ#NVRAMも参照)。 これはPC/AT互換機の分野からの慣習で、IBM PCシリーズではじめてリアルタイムクロックIC(RTC)が搭載されたPC/ATの、モトローラ製RTC ICであるMC146818に由来する。BIOSの設定は、このICの内蔵SRAMに記憶していた。このICは、電源切断時もボタン型電池などによるバッテリーバックアップで動作し続けられるよう、消費電力を低減する必要があったため、時計や電卓などの極省電力機器以外では当時まだ珍しかったCMOSプロセスで製造されていたことから、MC146818自体がCMOSと呼ばれるようになった。さらにこれが転じてBIOSの情報を記憶するメモリのことをCMOSと呼ぶようになった。 関連項目脚注注釈

出典

|