|

半精度浮動小数点数半精度浮動小数点数(はんせいどふどうしょうすうてんすう、英: half-precision floating point number)は浮動小数点方式で表現された数(浮動小数点数)の一種で、16ビット(2オクテット)の形式によりコンピュータ上で表現可能な浮動小数点数である。 IEEE 754-2008ではbinary16と名づけられている他、処理系や文脈によってs10e5やhalf、fp16などと表記される。 歴史FP16は当初、主にコンピュータグラフィックス用として提唱された、浮動小数点数フォーマットのひとつである[1]。 GPUにおいては、リアルタイム3次元コンピュータグラフィックス処理において単精度浮動小数点数に対するスループット向上などを目的に、DirectX 9.0 (Direct3D 9.0) APIとCg/HLSL(シェーディング言語)で利用可能なデータ形式として、NVIDIAとマイクロソフトが共同で策定し、GeForce FXやQuadro FXで採用したのが始まりである。ただし当時のFP16の主な目的は浮動小数テクスチャのデータ量を削減するためのフォーマットであり、FP16のハードウェアアクセラレーションをサポートしないハードウェアにおける インダストリアル・ライト&マジック社の研究の中で、広いダイナミックレンジと浮動小数点数の特徴を生かして光量の調整に向いていることが分かり、OpenEXRで採用された。 その後、IEEE 754rを経てIEEE 754-2008でbinary16として、データ交換とデータ容量削減を主目的とした保存用フォーマットとして採用された。 近年[いつ?]では、ハードウェアサポート(SIMD: Packed FP16)があれば高い演算性能 (FLOPS) が見込める上に、メモリ容量やディスク容量が節約できることから、ディープラーニングにおいて利用が活発化している。 用途誕生の経緯から、リアルタイムグラフィックス用途で利用されているほか、HDRレンダリング (High-Dynamic-Range Rendering) などプロダクション用途で利用が可能である。ダイナミックレンジを広くとることができることから、アニメーションやCGなどの用途で利用されることが多いが、一般的な画像ファイルフォーマットとして対応しているものは少なく、OpenEXRやDDSといった特殊な形式に限られる。 また、ハードウェアの支援があればスループットが劇的に向上し、かつ、nビットの乗算器の回路規模はn2log(n)に比例するので、仮数部11ビットの半精度浮動小数点数の乗算器の規模、すなわちチップに占める面積は、16ビットの整数乗算器の半分程度であり(ただし加減算に必要な、正規化のためのシフト処理は別途必要)、同一面積のチップに実装できる積和演算器の数も大幅に増やすことができる。モバイル向けGPUでは消費電力と性能と精度のバランスの観点から、既定でFP32よりもFP16が使われることが多い。重み付け係数を格納するストレージ容量の節約になることも相まって、並列度の高いディープラーニング用途において注目が集まっており、パーソナルコンピュータ/ワークステーション/サーバー向けにおいても対応GPUが増加し、FPGAでの実装や汎用的な信号処理用のアクセラレータの研究も進んでいる。 IEEE 754 半精度2進浮動小数点表現: binary16IEEE 754標準はbinary16を以下のように定めている。

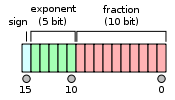

他のIEEE754浮動小数点表現と同様、指数部が全0でない限り黙示的な「1」のビットを仮数部に持つ(いわゆる「ケチ表現」)。このため仮数部に記録するのは10ビットだが11ビットの精度を持つ。より、これは十進数にしておよそ3桁の値となる。ビットは下図のように並ぶ。 指数部のエンコーディング半精度2進浮動小数点数の指数部はオフセット2進表現でエンコードされており、オフセット(IEEE 754における指数部バイアス)は15である。

よって、真の指数を得るためには、記録された指数から15を引けばよい。 記録された指数の0x00と0x1fは特別に扱われる。

半精度数の例浮動小数点数値のビット列を十六進法で表した例を以下に示す。これには符号、オフセットを加えた指数値、仮数値が含まれている。 3c00 = 1 3c01 = 1.0009765625、1より大きい最小の数 3c02 = 1.001953125 3fff = 1.9990234375、2より小さい最大の数 4000 = 2 c000 = -2 7bfe = 65472 7bff = 65504 (半精度数の正の最大値。符号なし16ビット整数の最大数(65535)と大差ない) fbff = -65504 (半精度数の負の最大値) 0400 = 2-14 ≈ 6.10352 × 10-5 (最小の正の正規化数) 0001 = 2-24 ≈ 5.96046 × 10-8 (最小の正の非正規化数) 0000 = 0 8000 = -0 7c00 = 正の無限大 fc00 = 負の無限大 3555 ≈ 0.33325... ≈ 1/3 1/3は切り下げられる。これは仮数部のビット数が奇数であるため(1/3は2進小数で0.01010101...)である。 対応状況ハードウェア

ソフトウェア

脚注注釈

出典

外部リンク

|

|||||||||||||||||||