|

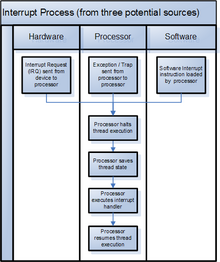

InterrupcióUna interrupció (també coneguda com a interrupció de maquinari o petició d'interrupció) és un senyal rebut pel processador d'un ordinador, indicant que ha d'interrompre el curs d'execució actual i passar a executar codi específic per tractar aquesta situació. Una interrupció suposa una pausa en l'execució del programa, desant l'estat actual del processador, per passar a executar una "subrutina de servei d'interrupció", que pertany al BIOS (Basic Input Output System). Les interrupcions sorgeixen de les necessitats que tenen els dispositius perifèrics d'enviar informació al processador principal d'un sistema de computació. La primera tècnica que es va utilitzar fou que el mateix processador s'encarregués de sondejar (polling) el dispositiu cada cert temps per esbrinar si tenia pendent alguna comunicació per a ell. Aquest mètode presentava l'inconvenient de ser molt ineficient, ja que el processador constantment consumia temps realitzant totes les instruccions de sondeig. El mecanisme d'interrupcions fou la solució que va permetre al processador desentendre's d'aquesta problemàtica, i delegar en el dispositiu la responsabilitat de comunicar-se amb el processador quan ho necessités. El processador, en aquest cas, no sondeja cap dispositiu, sinó que queda a l'espera que aquests l'avisin (l'interrompin) quan tinguin alguna cosa a comunicar-li (ja sigui una transferència d'informació, una condició d'error, un esdeveniment, etc.). Funcionament del mecanisme d'interrupcions Cada dispositiu que voleu comunicar-se amb el processador per interrupcions ha de tenir assignada una línia única capaç d'avisar a aquest que li requereix per a una operació. Aquesta línia és l'anomenada IRQ (Interrupt Request ", petició d'interrupció). Les IRQ són línies que arriben al controlador d'interrupcions, Un component maquinari dedicat a la gestió de les interrupcions, i que pot estar integrat en la UCP o ser un circuit separat connectat al processador principal. El controlador d'interrupcions ha de ser capaç d'activar o inhibir línies d'interrupció (operació anomenada comunament emmascarar per la utilització d'una màscara), I establir prioritats entre les diferents interrupcions habilitades. Quan diverses línies de petició d'interrupció s'activen a la vegada, el controlador d'interrupcions utilitzarà aquestes prioritats per escollir la interrupció sobre la qual informarà al processador principal. No obstant això hi ha interrupcions que no es poden emmascarar, o bé, les conegudes com interrupcions no emmascarar o NMI. Un processador principal (sense controlador d'interrupcions integrat) sol tenir una única línia d'interrupció anomenada habitualment INT. Aquesta línia és activada pel controlador d'interrupcions quan té una interrupció de servir. En activar aquesta línia, el processador consulta els registres del controlador d'interrupcions per a esbrinar quina IRQ és la que ha d'atendre. A partir del nombre de IRQ cerca al vector d'interrupcions què rutina ha de trucar per atendre una petició del dispositiu associat a aquesta IRQ. Les rutines d'interrupció generalment prenen un petit temps d'execució i la majoria no poden ser interrompudes quan s'estan atenent, perquè en entrar-hi s'emmagatzema l'estat dels registres en una pila i si s'interrompen moltes vegades, la pila es pot desbordar. Passos per al processament d'una IRQ: 1) Acabar l'execució de la instrucció màquina en curs. 2) Salva el valor de comptador de programa, PC, a la pila, de manera que en la CPU, en acabar el procés, pugui seguir executant el programa a partir de l'ultima instrucció. 3) La CPU salta a l'adreça on està emmagatzemada la rutina de servei d'interrupció (ISR, Interrupt Service Routine) i executa aquesta rutina que té com a objectiu atendre al dispositiu que va generar la interrupció. 4) Una vegada que la rutina de la interrupció acaba, el processador restaura l'estat que havia guardat a la pila en el pas 2 i torna al programa que s'estava usant anteriorment. Mecanisme d'interrupcions en un PCUn ordinador PC típic disposa en seu placa base d'un controlador d'interrupcions 8259 de Intel o d'un circuit integrat anàleg. Aquest dispositiu electrònic disposa de fins a 16 línies IRQ, numerades des del 00 fins al 15. A les noves plaques base aquest circuit està integrat junt amb la resta del chipset i permet fins a 24 interrupcions.

|